# **JWE980**

# 电能计量电路

### 概述

JWE980 是一种高准确度、容错电能测量集成电路,其技术指标达到了 IEC1036 规定 的准确度要求。

JWE980 只在 ADC 和基准源中使用模拟电路,所有其它信号处理(如相乘和滤波)都使用数字电路, 这使 JWE980 在恶劣的环境条件下仍能保持极高的准确度和长期稳定性。

JWE980 内部集成了一个新颖的故障检测机制,当线路发生故障时,JWE980 发出警告信号,并可以继续保持精确的计量。JWE980 通过连续的监测相线和零线上的电流,当两路电流值相差大于 12.5%时输出故障指示,并自动切换,采用两路电流中的较大值进行计量。

JWE980 引脚 F1 和 F2 以较低频率形式输出有功功率平均值,能直接驱动机电式计度器或与微控制器(MCU)接口。引脚 CF 以较高频率形式输出有功功率瞬时值,用于校验或与 MCU 接口。

JWE980 内部包含一个对 VDD 电源引脚的监控电路。在 VDD 上升到 4V 之前, JWE980 一直保持在复位状态。当 VDD 降到 4V 以下, JWE980 也被复位, 此时 F1, F2 和 CF 都没有输出。

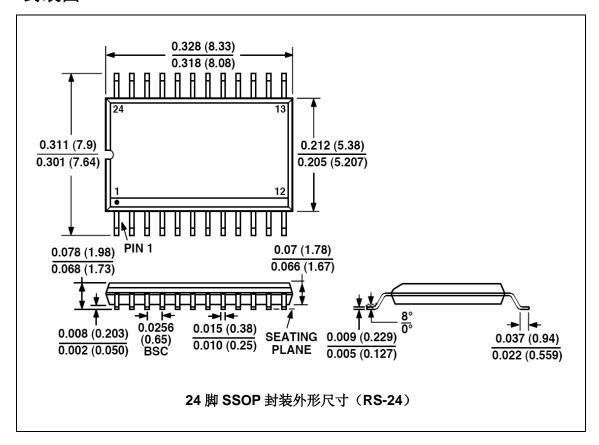

内部相位匹配电路使电压和电流通道的相位始终是匹配的,无论通道 1 内的高通滤波器 (HPF) 是接通的还是断开的。内部的空载阈值特性保证 JWE980 在空载时没有潜动。 JWE980 为 24 脚 SSOP 封装形式。

### 特点

- 高准确度,达到 50Hz/60Hz IEC 687/1036 标准的准确度要求,在 500:1 的动态范围内 误差小于 0.1%:

- 有功功率平均值从 JWE980 引脚 F1 和 F2 以频率方式输出;

- 有功功率瞬时值从引脚 CF 以较高频率方式输出,能用于仪表校验;

- 支持2线配电系统故障检测,连续监测相线和零线的电流;

- JWE980 采用两路电流(相线和零线)中的较大值进行计量,即使在线路发生故障时也是如此;

- 两个逻辑输出引脚 FAULT 和 REVP 能指示错误接线;

- FI 和 F2 能直接驱动机电式计度器和两相步进电机;

- 电流通道中的可编程增益放大器 (PGA) 使仪表能使用小阻值的分流电阻;

- 在环境和时间有很大变化的条件下,采用专用模数转换器(ADC)和数字信号处理 (DSP)仍保证高准确度;

- 片内设有电源监控电路;

- 片内带有防潜动功能(空载阈值);

- 片内基准电压 2.5V±8% (温度系数典型值 30ppm/℃), 能为外部电路提供基准;

- 片内带有对温度敏感度很小的高稳定性振荡器。

- +5V 单电源、低功耗(典型值 15mW);

- 低成本 CMOS 工艺。

### 引脚特征

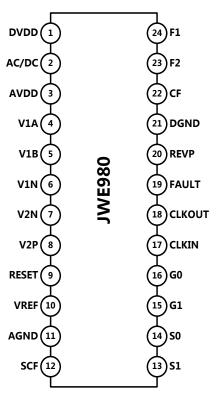

图 (1) 引脚排列图 (SSOP24 封装)

# 引脚描述

| 引脚号    | 符号                    | 说明                                                                                                                                             |

|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | DVDD                  | 数字电源引脚。该引脚提供 JWE980 数字电路的电源,正常工作电源电压应保持在 5V±5%,该引脚应使用 10μ F 电容并联 100nF 瓷介电容进行去耦。                                                               |

| 2      | AC/DC                 | 高通滤波 HPF 选择引脚。当该引脚输入高电平时,通道 1(电流通道)内的 GPF 被选通,该滤波器所涉及的相位响应在 45Hz 至 1kHz 范围内在片内已得到补偿。在电能计量的应用中,应使 GPF 选通。                                       |

| 3      | AVDD                  | 模拟电源引脚。该引脚提供 JWE980 模拟电路的电源,正常工作电源电压应保持在 5V±5%,为使电源的纹波和噪声减小到最低程度,该引脚应使用 10µ F 电容并联 100nF 资介电容进行去耦。                                             |

| 4, 5   | V1A, V1B              | 通道 1(电流通道)的模拟输入,该输入为全差分电压输入。正常工作相对 V1N 的最大信号电平为±470mV,相对 AGND 的最大信号电平为±1V。这两个管脚内部都有 ESD 保护电路,能承受±6V 的过电压而不造成永久性损坏。                             |

| 6      | V1N                   | 差分电压信号 V1A,V1B 的负输入端。相对 AGND 的最大信号电平为 ±1V。通道 1 有一个 PGA, 其增益选择见表 I。这个引脚内部都有 ESD 保护电路,能承受±6V 的过电压,而不造成永久性损坏。                                     |

| 7, 8   | V2N, V2P              | 通道 2(电压通道)的负、正模拟输入引脚。完全差动输入方式,正常工作最大输入电压为±660mV,相对于 AGND 的最大信号电平为±1V。两个引脚内部都有 ESD 保护电路,这两个引脚能承受±6V 的过电压,而不造成永久性损坏。                             |

| 9      | RESET                 | 复位引脚。当为低电平时,ADC 和数字电路保持复位状态,在 RESET 的下降沿,清除 JWE980 内部寄存器。                                                                                      |

| 10     | REF <sub>IN/OUT</sub> | 基准电压的输入、输出引脚。片内基准电压标称值为 2.5V±8%,典型温度系数为 30 ppm/℃。外部基准源可以直接连接到该引脚上。无论用内部还是外部基准源,该引脚都应使用 10µ F 钽电容和 100nF 瓷介电容对 AGND 进行去耦。                       |

| 11     | AGND                  | 这是 JWE980 模拟电路(即 ADC 和基准源)的接地参考点,该引脚误码连接到印刷电路板的模拟接地面。模拟接地面是所有模拟电路的接地参考点,如抗混叠滤波器、电流和电压传感器等。为了有效地抑制噪声,模拟接地面与数字接地面只应有一点连接。星形接地方法有助于使数字电流噪声远离模拟电路。 |

| 12     | SCF                   | 校验频率选择。该引脚的逻辑输入电平确定 CF 引脚的输出频率,如何选择校验频率见表 IV。                                                                                                  |

| 13, 14 | S1, S0                | 这两个引脚的逻辑输入用来选择数字/频率转换系数,这为电度表的设计提供了很大灵活性,详见为电度表应用选择频率部分。                                                                                       |

| 15, 16 | G1, G0                | 这两个引脚的逻辑输入用来选择通道 1 的增益。可能的增益是 1, 2, 8 和 16, 详见模拟输入部分。                                                                                          |

| 引脚号    | 符号     | 说明                                                                                                                                        |

|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 17     | CLKIN  | 外部时钟可从该引脚接入,也可把一个石英晶体接在 CLKIN 和 CLKOUT 之间,为 JWE980 提供时钟源,规定时钟频率为 3.579545MHz。作为石英晶体负载的 33pF 瓷介电容应和振荡器门电 路连接。                              |

| 18     | CLKOUT | 如上所述,可把一个石英晶体接在 CLKIN 和 CLKOUT 之间,为 QD7755 提供一个时钟源。当 CLKIN 上接有外时钟时 CLKOUT 引脚 能驱动一个 CMOS 负载。                                               |

| 19     | FAULT  | 当故障情况(即 V1A 和 V1B 两个信号通道的差值超过 12.5%)发生后,该管脚输出高电平。故障情况消除后,该管脚输出低电平。                                                                        |

| 20     | REVP   | 当检测到负功率时,即电压和电流信号的相位差大于90°时,该引脚输出逻辑高电平。该输出没有被锁存,当再次检测到正功率时,该引脚的输出复位。该输出的逻辑状态随CF输出脉冲同时变化。                                                  |

| 21     | DGND   | 这是 JWE980 数字电路(即乘法器、滤波器和数字频率转换器)的接地参考点。该引脚应连接到印刷电路板的数字接地面,数字接地面是所有数字电路(如机械或数字计度器、微控制器和 LED 显示器)的接地参考点。为了有效地抑制噪声,模拟接地面与数字接地面只应有一点连接,如星形接地。 |

| 22     | CF     | 频率校验输出引脚。其输出频率反映瞬时有功功率的大小,常用于仪<br>表校验,参见 SCF 引脚说明。                                                                                        |

| 23, 24 | F2, F1 | 低频逻辑输出脚,输出频率反应平均有功功率的大小。这两个逻辑输<br>出可以直接驱动机电式计度器或两相步进电机,详见传递函数部分。                                                                          |

# 电气特性

(VDD= 5V±5%,GND=0V,使用片内基准源,CLKOSC=3.58MHz,温度范围=-40~+85℃)

| 参 数                          | 规格   | 单 位         | 测试条件及注释                     |

|------------------------------|------|-------------|-----------------------------|

| 精度 1,2                       |      |             |                             |

| 通道1的测量误差1                    |      |             | 通道 2 为满度输入(±660mV),+25℃     |

| G=1                          | 0.1  | %读数 typ     | 动态范围 <b>500</b> : 1         |

| G=16                         | 0.1  | %读数 typ     | 动态范围 <b>500</b> : 1         |

| 两个通道间的相位误差 1                 |      |             |                             |

| V1 超前 37° (PF=0.8 容性)        | ±0.1 | 度(°)max     | AC/DC =0 和 AC/DC=1          |

| V1 滯后 60° (PF=0.5 感性)        | ±0.1 | 度(°) max    | AC/DC=0 和 AC/DC=1           |

| 交流电源抑制 1                     |      |             | AC/DC=1, S0=S1=1, G0=G1=0   |

| 输出频率变化(CF)                   | 0.2  | %读数 typ     | V1=V2=100mVrms, 50Hz        |

|                              |      |             | VDD 加有 200 mV rms,100Hz 纹波  |

| 直流电源抑制 1                     |      |             | AC/DC=1, S0=S1=1, G0=G1=0   |

| 输出频率变化(CF)                   | ±0.3 | %读数 typ     | V1=V2=100mV rms             |

|                              |      |             | VDD =5V±250mV               |

| 故障检测                         |      |             | 见故障检测部分                     |

| 故障检测阈值                       | 12.5 | % typ       | (V1A 或 V1B 激活)              |

| 输入切换阈值                       | 14   | %激活通道 typ   | <br>  (V1A 或 V1B 激活)        |

| 故障模式计量精确度                    |      |             |                             |

| V1A 激活,V1B=AGND              | 0.1  | %读数 typ     | <br>  动态范围 500: 1           |

| V1B 激活,V1A=AGND              | 0.1  | %读数 typ     | 动态范围 500: 1                 |

| 故障检测延迟                       | 3    | Second typ  |                             |

| 输入切换延迟                       | 3    | Second typ  |                             |

| 模拟输入                         |      |             |                             |

| 最大信号电平                       | ±1   | Vmax        | V1P,VIN,V2N 和 V2P 对 GND 的电压 |

| 直流输入阻抗                       | 390  | kΩ min      | CLKOSC=3.58MHz              |

| -3dB 带宽                      | 14   | kHz typ     | CLKOSC/256, CLKOSC=3.58MHz  |

| ADC 失调误差 <sup>1,2</sup>      | ±16  | mV max      |                             |

| 增益误差 1                       | ±4   | %理想值 typ    | <br>  外基准源 2.5V,G=1         |

|                              |      |             | V1=660mVdc, V2=660mV dc     |

| 增益匹配误差 1                     | ±0.2 | %理想值 typ    | 外基准源 2.5V                   |

| 基准输入                         |      |             |                             |

| REF <sub>IN/OUT</sub> 输入电压范围 | 2.7  | V max       | 2.5V+8%                     |

| • • • • • • •                | 2.3  | V min       | 2.5V-8%                     |

| 输入阻抗                         | 3.2  | k Ω min     |                             |

| 输入电容                         | 10   | pF max      |                             |

| 片内基准源                        |      |             | 标称值 2.5V                    |

| 基准电压误差                       | ±200 | mV max      |                             |

| 温度系数                         | 30   | ppm/℃ typ   |                             |

|                              |      | 11 -2 - 3/6 |                             |

|                              |      |             |                             |

|                              |      |             |                             |

| 参 数                            | 规格   | 单 位     | 测试条件及注释                            |

|--------------------------------|------|---------|------------------------------------|

| 时钟输入                           |      |         | 注意: 所有指标 CLKOSC 均为 3.58MHz         |

| 输入时钟频率                         | 4    | MHz max |                                    |

|                                | 1    | MHz min |                                    |

| 逻辑输入3                          |      |         |                                    |

| SCF, SO, S1, AC/DC             |      |         |                                    |

| RESET,G0和G1                    |      |         |                                    |

| 输入高电平,V <sub>INH</sub>         | 2.4  | V min   | VDD=5V±5%                          |

| 输入低电平, <b>V</b> <sub>INL</sub> | 0.8  | V max   | VDD=5V±5%                          |

| 输入电流,V <sub>IN</sub>           | ±3   | μ A max | 典型值 10nA,V <sub>IN</sub> =0V 至 VDD |

| 输入电容,V <sub>IN</sub>           | 10   | pF max  |                                    |

| 逻辑输出3                          |      |         |                                    |

| F1 和 F2                        |      |         |                                    |

| 输出高电平, <b>V</b> OH             | 4.5  | V min   | I <sub>SOURCE</sub> =10mA,VDD=5V   |

| 输出低电平, <b>V</b> oL             | 0.5  | V max   | I <sub>SINK</sub> =10mA, VDD=5V    |

| CF 和 REVP                      |      |         |                                    |

| 输出高电平, <b>V</b> OH             | 4    | V min   | I <sub>SOURCE</sub> =10mA, VDD=5V  |

| 输出低电平, <b>V</b> oL             | 0.5  | V max   | I <sub>SINK</sub> =10mA,VDD=5V     |

| 电源                             |      |         | 为达到规定指标对电源的要求                      |

| VDD                            | 4.75 | V min   | 5V-5%                              |

|                                | 5.25 | V max   | 5V+5%                              |

| I <sub>DD</sub>                | 4    | mA max  | 典型值 3.5mA                          |

|                                | 3    | mA min  | 典型值 3.5mA                          |

# 极限参数

| VDD 相当于 GND 电压0.3V~+7V                      |

|---------------------------------------------|

| 模拟输入 VIA,V1B,VIN,V2P 和 V2N 相当于 GND 电压6V∼+6V |

| 基准输入电压相当于 GND0.3V~VDD+0.3V                  |

| 数字输入电压相当于 GND                               |

| 数字输出电压相当于 GND                               |

| 工作温度范围: 工业级40℃~+85℃                         |

| 存储温度范围                                      |

| 结温 +150℃                                    |

| 24 脚 SSOP 封装散耗功率 450mW                      |

| 热阻 112℃/w                                   |

| 焊接温度汽相焊接(60 秒) +215℃                        |

| 红外焊接(15 秒) +220℃                            |

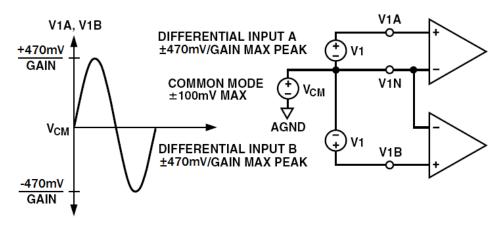

### 模拟输入

#### 通道 V1 (电流通道)

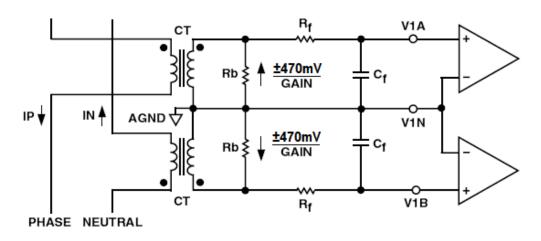

线路电流传感器的输出电压接到 JWE980 的通道 V1,该通道采用完全差动输入。 V1A,V1B 为正输入端,V1N 为负输入端。

通道 1 的最大差动峰值电压应小于 470mv。应当注意,通道 1 有一个 PGA,其增益可由用户选择为 1 或 16 (见表 1),这使传感器接口的设计大为简单。

图(5)通道1的最大信号电平(G=1)

图 (5) 示出了 V1A,V1B 和 VIN 引脚的最大信号电平,最大差动电压是(470mV),由增益选择而定。在这两引脚上的差动信号必须以一个共模端作为参考点,如 GND.最大共模信号为(100mV),如图 5 所示。

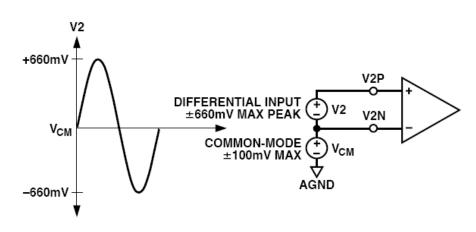

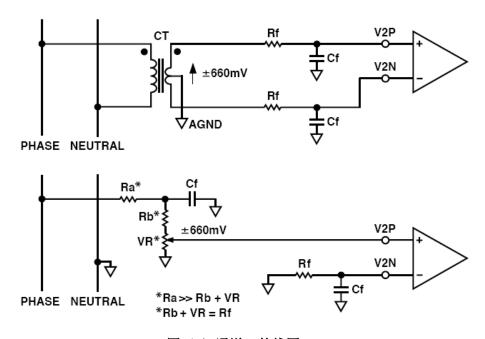

#### 通道 V2(电压通道)

线路电压传感器的输出接到 JWE980 的通道 V2,该通道的最大差动峰值电压±660mV,图(6)示出了允许连接到 JWE980 通道 2 的最大信号电平。

图 (6) 通道 2 的最大信号电平

加在通道 2 上的差动电压信号必须以一个共模端作为参考点(通常是 GND),最大共模电压为(100mV)。然而,当共模电压为 0V 时能获得最好的测量结果。

#### 典型接线图

图(7)示出了通道 1 的电路接线图,由于相线和零线上的电流可能会有较大的偏差,本例选择电流互感器(CT)作为电流传感器监视相线和零线上的电流。应当注意,这里通道 1 的两个 CT 都是相对 AGND,所以其共模电压为 0V。CT 的变比和负载电阻 Rb 的大小根据差动峰值电压而定,即在最大负载条件下,通道 1 的差动峰值电压应为±470mV/G.

图 (7) 通道 1 的典型接线图

图(8) 示出了通道 2 两种电路接线方法。第一种方法是使用一个电压互感器(PT),它能使 JWE980 与主电网完全隔离。第二种方法是以电网的中线(零线)为基准,用一个电阻分压器提供与线路电压成正比的电压信号,调整 Ra,Rb 和 VR 的比值能很方便地完成仪表的增益校验。

图(8)通道2的线图

| 表 1        | 涌道1 | 的增   | 益选择   |

|------------|-----|------|-------|

| <b>双 I</b> |     | ロリノ甘 | イカルガギ |

| G1 | G0 | 增益 | 最大差动信号 |

|----|----|----|--------|

| 0  | 0  | 1  | ±470mv |

| 0  | 1  | 2  | ±235mv |

| 1  | 0  | 8  | ±60mv  |

| 1  | 1  | 16 | ±30mv  |

### 故障检测

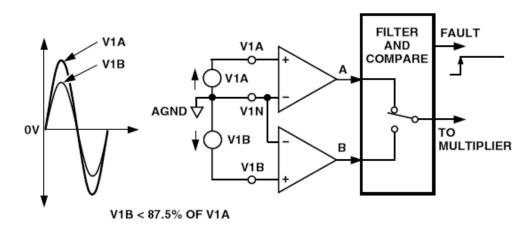

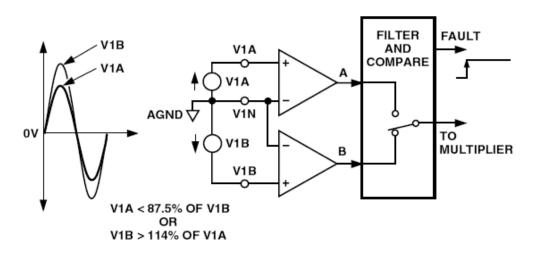

JWE980 集成了一个故障检测机制,当线路出现故障时,JWE980 能输出故障指示,并继续保持精确计量。故障检测功能工作在 45Hz 到 55Hz 的工频范围内。JWE980 通过连续的监测相线和零线的电流,当两根线上的电流差值超过 12.5%时,从 FAULT 脚输出故障指示,同时,比较 V1 两个通道的输入信号,使用较大的信号进行计量。

上电后, JWE980 默认选通 V1A 通道。若上电时 V1A 和 V1B 两个通道的差值大于 12.5%, 1s 后,故障指示灯(FAULT)将会置高。另外,如果 V1B 的信号大于 V1A 的信号, JWE980 会选择 V1B 做为输入。

当 V1 通道的输入电压信号小于 0.5%的满幅输入范围后。由于噪声的影响可能会导致故障检测出错,此时,TWE980 将自动禁用故障检测功能。

#### V1A 大于 V1B 的故障情况

V1B 大于 V1A 的故障情况

# 输出频率

表 2 F<sub>1-4</sub> 的频率选择(CLKOSC=3.579MHz)

| S1 | S0 | F <sub>1-4</sub> (Hz) | 分频系数                   |

|----|----|-----------------------|------------------------|

| 0  | 0  | 1.7                   | <b>2</b> <sup>21</sup> |

| 0  | 1  | 3.4                   | 2 <sup>20</sup>        |

| 1  | 0  | 6.8                   | 2 <sup>19</sup>        |

| 1  | 1  | 13.6                  | 2 <sup>18</sup>        |

#### 表 3 F1 和 F2 的最高输出频率

| 61 | S1 S0 | 最高输出频率 |      |  |

|----|-------|--------|------|--|

| 31 |       | 直流输入   | 交流输入 |  |

| 0  | 0     | 0.68   | 0.34 |  |

| 0  | 1     | 1.36   | 0.68 |  |

| 1  | 0     | 2.72   | 1.36 |  |

| 1  | 1     | 5.44   | 2.72 |  |

#### 表 4 CF 的最高输出频率(交流信号)

| a - Has Misa internal Compiler As |    |    |                       |                 |

|-----------------------------------|----|----|-----------------------|-----------------|

| SCF                               | S1 | S0 | F <sub>1-4</sub> (Hz) | CF 的最高输出频率(Hz)  |

| 1                                 | 0  | 0  | 1.7                   | 128×F1,F2=43.52 |

| 0                                 | 0  | 0  | 1.7                   | 64×F1,F2=21.76  |

| 1                                 | 0  | 1  | 3.4                   | 64×F1,F2=43.52  |

| 0                                 | 0  | 1  | 3.4                   | 32×F1,F2=21.76  |

| 1                                 | 1  | 0  | 6.8                   | 32×F1,F2=43.52  |

| 0                                 | 1  | 0  | 6.8                   | 16×F1,F2=21.76  |

| 1                                 | 1  | 1  | 13.6                  | 16×F1,F2=43.52  |

| 0                                 | 1  | 1  | 13.6                  | 8×F1,F2=21.76   |

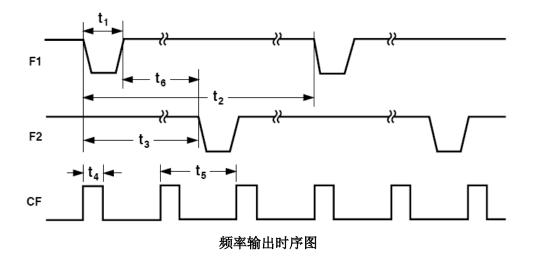

# 时序特性

(VDD= 5V±5%, GND=0V, 使用片内基准源, CLKOSC=3.58MHz, 温度范围=-40~+85℃)

| 参 数                   | 尾标 A,B             | 单 位 | 测试条件及注释             |

|-----------------------|--------------------|-----|---------------------|

| T <sub>1</sub> 注(1)   | 275                | ms  | F1 和 F2 的底电平脉宽      |

| T <sub>2</sub>        | 见表 3               | s   | 输出脉冲周期,见传递函数部分      |

| T <sub>3</sub>        | 1/2 T <sub>2</sub> | s   | F1 下降沿和 F2 下降沿之间的时间 |

| T <sub>4</sub> 注(1,2) | 90                 | ms  | CF 输出的高电平脉宽         |

| T <sub>5</sub>        | 见表 4               | s   | CF 输出脉冲周期,见传递函数部分   |

| T <sub>6</sub>        | CLKOSC/4           | s   | F1 和 F2 脉冲之间的最小时间   |

注:(1) 在较高的输出频率时 F1,F2 和 CF 的脉宽不固定。

(2) 在高频方式下, CF 脉宽总是 18µs。

### 封装图